## Synthesis of CMOS Gates

Let's consider the design synthesis of CMOS gates by considering the design synthesis of PUN and PDN separately.

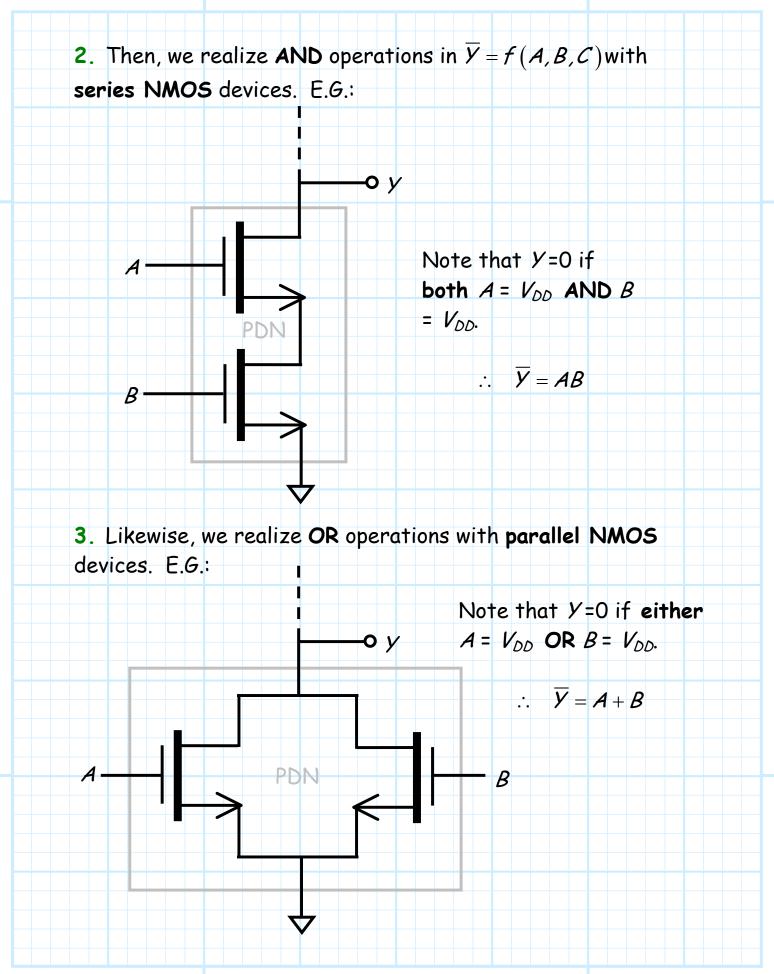

## PDN Design Synthesis

1. If the PDN is conducting, then the output will be low. Thus, we must find a Boolean expression for the complemented output  $\overline{Y}$ .

In turn, the PDN can only be conducting **if one or more** of the NMOS devices are **conducting**—and **NMOS** devices will be conducting (i.e., **triode** mode) when the **inputs are high** ( $V_{GSN} = V_{DD}$ ).

Thus, we must express  $\overline{Y}$  in terms of un-complemented inputs A, B, C, etc (i.e.,  $\overline{Y} = f(A, B, C)$ ).

e.g.,  $\rightarrow \overline{Y} = A + BC$

This step may test our **Boolean algebraic** skills!

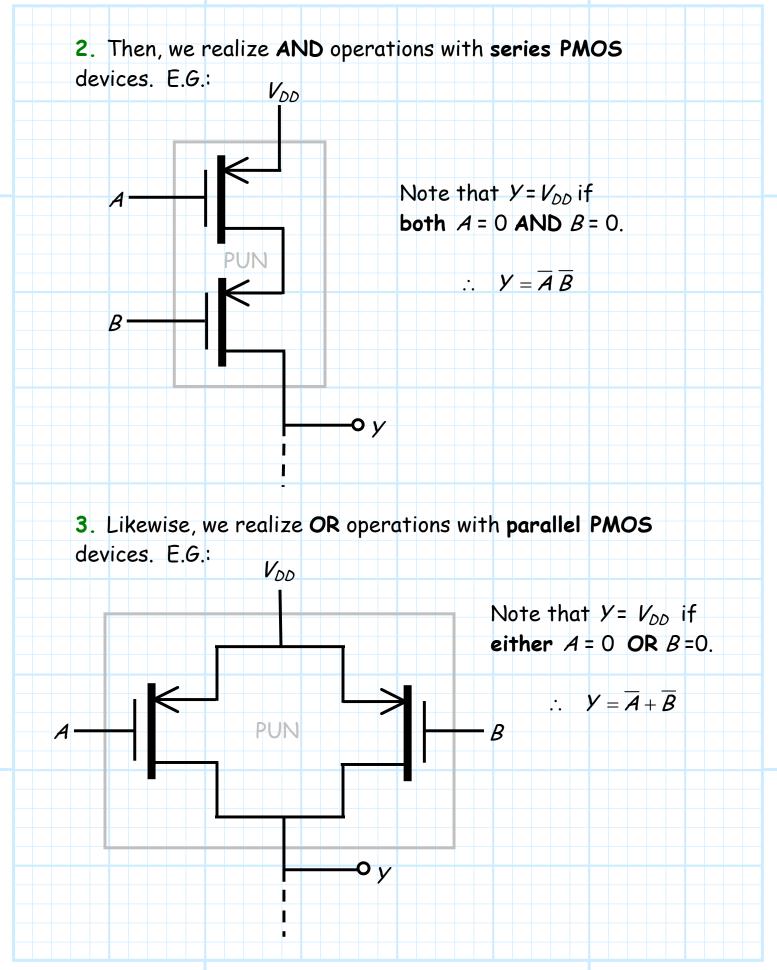

## PUN Design Synthesis

1. If the PUN is conducting, then the output will be high. Thus, we must find a Boolean expression for the uncomplemented output Y.

In turn, the PUN can only be conducting **if one or more** of the PMOS devices are **conducting**—and **PMOS** devices will be conducting (i.e., **triode** mode) when the **inputs are low** ( $V_{GSP}$ = - $V_{DD}$ ).

Thus, we **must** express Y in terms of complemented inputs  $\overline{A}, \overline{B}, \overline{C}$ , etc (i.e.,  $Y = f(\overline{A}, \overline{B}, \overline{C})$ ).

e.g.,

$$\rightarrow Y = \overline{A} + \overline{B}\overline{C}$$

This step may test our Boolean algebraic skills!